已知真值表 怎么画d触发器

一、理解D触发器基本概念

D触发器是一种具有数据输入端(D)、时钟输入端(CLK)以及输出端(Q和\(\overline{Q}\))的时序逻辑电路基本单元,它的主要特性是在时钟信号的有效边沿到来时,能将数据输入端D的信号传递到输出端Q,即实现数据的暂存功能,其真值表通常反映了在不同输入条件下输出状态的变化规律。

二、分析给定的真值表

假设我们有以下简化的D触发器真值表(实际真值表可能因具体电路设计细节有所不同,此处仅为示例):

| CLK | D | Q(现态) | Q(次态) |

| ↑ | X | 0 | 1 |

| ↑ | X | 1 | 0 |

| ↓ | X | 0 | 0 |

| ↓ | X | 1 | 1 |

这里“↑”表示时钟信号的上升沿,“↓”表示时钟信号的下降沿,“X”代表该输入条件对输出次态无影响,“Q(现态)”是时钟信号变化前输出端的状态,“Q(次态)”是时钟信号变化后输出端的状态。

三、根据真值表绘制D触发器图形符号及标注逻辑关系

1、绘制基本图形符号

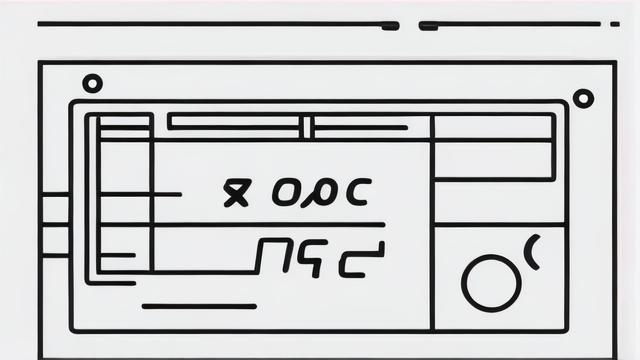

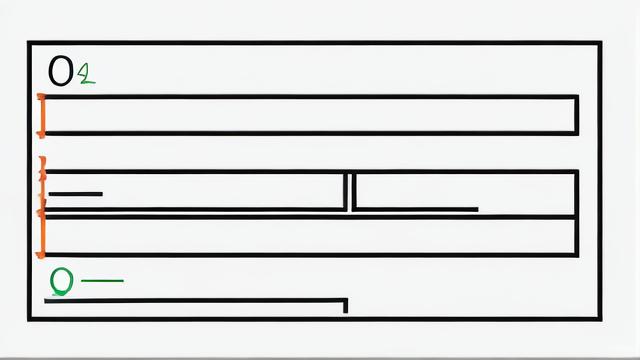

D触发器在电路图中通常用特定的图形符号来表示,它是一个矩形,左边有数据输入端D和时钟输入端CLK,右边有一对互补的输出端Q和\(\overline{Q}\),图形大致如下:

++

| D |

| |

CLK| | Q

| |

++2、标注逻辑关系

根据真值表中体现出的逻辑关系,在图形符号旁边进行标注,对于上述示例真值表,可以看出在时钟上升沿时,输出Q的次态等于输入D,这体现了D触发器最基本的逻辑功能,可在图形符号旁标注“Q(次态)=D(上升沿)”。

四、完善电路连接示意(考虑实际应用情况)

在实际电路中,D触发器会与其他元件相连接来构成更复杂的电路系统,数据输入端D可能会连接到某个数据总线或者逻辑门电路的输出端,时钟输入端CLK会连接到时钟信号产生电路等,但仅从根据真值表画D触发器本身来说,重点关注上述图形符号及基本逻辑关系的标注即可体现其主要功能特点。

通过分析真值表确定D触发器在时钟信号作用下输入与输出之间的逻辑关系,然后按照标准的图形符号绘制方法画出D触发器,并准确标注相应的逻辑关系,就完成了根据真值表画D触发器的操作。

FAQs

问题一:如果真值表中时钟信号的有效边沿既有上升沿又有下降沿,该如何标注逻辑关系呢?

答:这种情况下,需要分别标注出上升沿和下降沿对应的逻辑关系,若上升沿时Q(次态)=D,下降沿时Q保持不变,那就标注“Q(次态)=D(上升沿),Q(次态)=Q(现态)(下降沿)”。

问题二:不同型号的D触发器真值表可能会有细微差别,画图时该怎么处理呢?

答:要先仔细分析给定的具体真值表,找出其独特的逻辑关系,然后按照分析结果准确在图形符号旁进行标注,虽然整体的图形符号是类似的,但标注的逻辑关系一定要与所给真值表完全契合,确保能准确反映该特定D触发器的功能特点。

作者:豆面本文地址:https://www.jerry.net.cn/articals/34267.html发布于 2025-02-23 01:14:28

文章转载或复制请以超链接形式并注明出处杰瑞科技发展有限公司