Altera FPGA 学习全攻略 (Intel FPGA Edition)

第一部分:基础准备与核心概念

在开始动手之前,必须理解一些核心概念,这就像学开车前要先了解交通规则和汽车构造一样。

什么是 FPGA?

- 定义:现场可编程门阵列,它是一种半定制化的芯片,与 ASIC(专用集成电路)不同,FPGA 可以被用户反复编程和配置,实现特定的数字逻辑电路。

- 核心思想:通过硬件描述语言 编写代码,来“搭建”出你想要的数字电路,而不是像 CPU 那样执行软件指令,这使其在并行处理、低延迟方面具有巨大优势。

FPGA vs. CPU / MCU

- CPU/MCU:冯·诺依曼架构,顺序执行指令,擅长复杂的逻辑控制和通用计算。

- FPGA:哈佛架构,并行执行硬件电路,擅长大规模并行数据处理、高速信号采集、实时逻辑控制。

- 通俗比喻:CPU 像一个“大厨”,按菜谱(程序)一步步做菜,FPGA 像一个“流水线工厂”,每个工位(逻辑门)都在同时工作,效率极高。

Altera vs. Intel

- 历史:Altera 是一家非常著名的 FPGA 公司,其 Cyclone、Arria、Stratix 系列产品广受欢迎。

- 现状:2025 年,Intel 收购了 Altera,现在我们所说的 Altera FPGA,其官方名称是 Intel FPGA,芯片型号(如 Cyclone 10 GX)和开发软件(如 Quartus Prime)基本沿用 Altera 的体系,您可以继续使用 "Altera" 这个词来搜索资料,但新项目应关注 Intel FPGA。

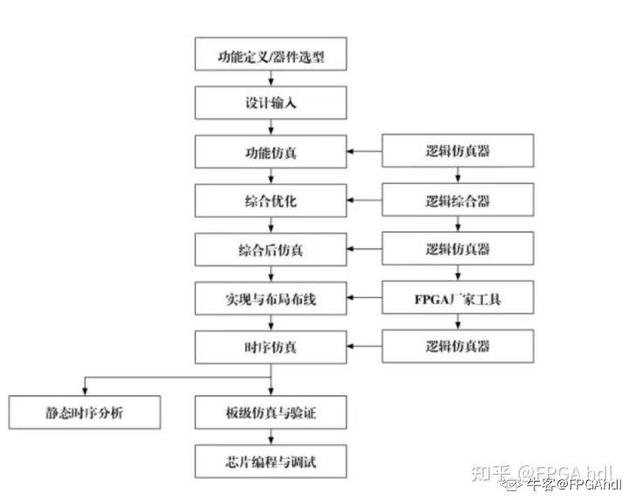

FPGA 开发基本流程 这是一个经典的“四步法”:

- 设计输入:使用 HDL (Verilog/VHDL) 或图形化方式描述你的电路。

- 功能仿真:不涉及硬件,只验证代码的逻辑是否正确,这是最重要的一步,能提前发现 90% 的错误。

- 综合:将 HDL 代码翻译成由 FPGA 内部基本逻辑单元(LUT, FF)组成的网表。

- 实现:包括布局布线,将网表适配到具体的 FPGA 芯片物理位置上,并生成最终的配置文件。

- 时序仿真:在综合和实现后,考虑实际硬件的延迟进行仿真,验证电路是否满足时序要求。

- 配置/烧录:将最终生成的配置文件通过 JTAG 或 AS 模式下载到 FPGA 芯片中,使其运行你设计的电路。

第二部分:核心开发工具

工欲善其事,必先利其器,FPGA 开发离不开强大的软件工具。

核心开发环境:Intel Quartus Prime 这是 Intel 官方的、免费的 FPGA 开发套件,它集成了设计输入、综合、仿真、时序分析、烧录等所有功能。

- 版本选择:

- Quartus Prime Lite Edition (免费版):支持 Intel 中低端 FPGA 系列,如 Cyclone® IV, V, 10 GX, MAX® 10,对于初学者和绝大多数项目来说,完全足够。

- Quartus Prime Standard/Pro Edition (付费版):支持高端系列,并提供更多高级功能和优化,初学者无需考虑。

- 下载地址:Intel 官网 Quartus Prime 下载页面

仿真工具:ModelSim Quartus 自带了一个简化版的 ModelSim (ModelSim-Altera),对于初学者,用它进行功能仿真就足够了。

- 更高级的选择:ModelSim SE (Standard Edition) 或 Questa Simulator,功能更强大,支持 SystemVerilog 等高级验证语言,初学阶段无需安装。

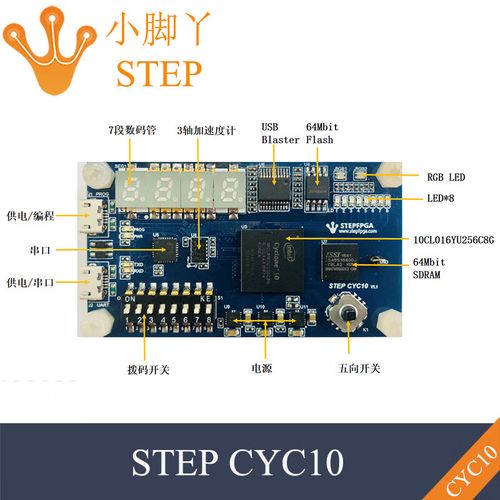

硬件平台 光有软件不行,你需要一块 FPGA 开发板来运行和验证你的设计。

- 推荐选择:

- Intel 官方开发板:如 DE10-Nano (基于 Cyclone 10 GX),资料最全,社区最活跃,是入门首选。

- 第三方开发板:如 Terasic 的 DE0-CV, DE10-Lite 等,也基于 Intel FPGA,同样优秀。

- 选择建议:初学者务必选择一块有详细文档、示例丰富、社区支持好的开发板。

第三部分:学习路径与实战项目

这是教程的核心,我们将从零开始,逐步深入。

入门与环境搭建 (预计 1-2 周)

- 安装软件:下载并安装 Quartus Prime Lite Edition,注意安装时勾选必要的组件,如

ModelSim-Altera。 - 熟悉 Quartus 界面:打开 Quartus,了解其主界面,特别是

Project Navigator(工程导航器)、Chip Planner(芯片规划器) 和Tcl Console(脚本控制台)。 - 点亮第一个 LED:这是 FPGA 开发的 "Hello World"。

- 目标:通过拨动开关,控制板载 LED 的亮灭。

- 步骤:

a. 创建新工程,选择你的开发板型号。

b. 使用

Block Design或直接编写 Verilog 代码,实现一个简单的组合逻辑(将开关的值直接赋给 LED)。 c. 进行编译。 d. 使用Quartus Programmer将配置文件烧录到 FPGA 中。 e. 在开发板上验证结果。

硬件描述语言 与基础逻辑 (预计 2-4 周)

这是 FPGA 的“内功心法”,你需要掌握 Verilog 或 VHDL 的一种。Verilog 在业界更常用,推荐初学者选择 Verilog。

-

学习 Verilog 语法:

- 模块:

module和endmodule,是设计的基本单元。 - 端口:

input,output,inout。 - 数据类型:

reg(用于存储,在 always 块中赋值),wire(用于连接,在 assign 中赋值)。 - 运算符:, ,

&, , ,<<,>>等。 - 结构:

- 组合逻辑:

assign语句(持续赋值)、always @(*)块(敏感列表为 表示任何信号变化都执行)。 - 时序逻辑:

always @(posedge clk)或always @(negedge clk)块(在时钟的上升沿或下降沿执行),用于实现寄存器、计数器、状态机等。

- 组合逻辑:

- 模块:

-

基础项目实践:

- 项目1:按键消抖:机械按键在按下和释放时会产生毛刺,学习用状态机或计数器来稳定按键信号。

- 项目2:分频器:将 FPGA 上的高频时钟(如 50MHz)分频成较低频率的时钟(如 1Hz)。

- 项目3:流水灯:让 LED 依次点亮,形成流动效果。

- 项目4:简单计数器:实现一个从 0 到 9 的计数器,并在数码管上显示。

进阶模块与接口 (预计 1-2 个月)

掌握了基础逻辑,现在开始学习如何让 FPGA 与外部世界交互。

- 状态机:FPGA 设计的灵魂,学习

Moore型和Mealy型状态机,用于实现复杂的控制逻辑,如交通灯、通信协议等。 - 存储器:

- ROM:用于存储固定的数据,如查表法、字库。

- RAM:用于临时存储数据,实现数据缓存。

- FIFO:先进先出队列,用于跨时钟域的数据传输。

- 常用接口协议:

- UART (串口):实现 FPGA 与 PC 之间的串口通信,是调试的利器。

- I2C / SPI:用于连接各种传感器、EEPROM、Flash 等外设。

- GPIO:最通用的输入输出,控制继电器、读取传感器等。

- IP 核的使用:IP 核是预定义好的、经过验证的功能模块(如 PLL 锁相环、DDR SDRAM 控制器、Nios II 软核处理器),学习在 Quartus 中调用这些 IP 核,能极大提高开发效率。

综合实战项目 (长期)

将所学知识融会贯通,完成一个完整的项目。

- 项目1:VGA 图像显示:在显示器上显示简单的彩色条纹或文字,这会涉及到时序生成、颜色编码等知识。

- 项目2:数字时钟:结合计数器、分频器和数码管/液晶屏,实现一个带有时、分、秒显示的电子钟。

- 项目3:简易 CPU:用 Verilog 实现一个简单的 8 位或 16 位 RISC 架构 CPU,并在 FPGA 上运行你编写的汇编程序,这是对数字逻辑理解的终极考验。

- 项目4:图像处理:从摄像头采集图像数据,在 FPGA 上实现简单的灰度化、边缘检测等算法。

第四部分:推荐学习资源

-

官方资源 (最权威)

- Intel 官方文档:Quartus Prime Handbook, Volume 1-5,是工具使用的圣经。

- 官方培训课程:Intel eLearning 平台有免费的官方视频课程。

- 开发板官方资料:DE10-Nano 等开发板的官方手册、原理图和示例代码,必须仔细阅读。

-

在线教程与社区

- Bilibili (B站):搜索 “FPGA Verilog入门”、“DE10-Nano 教程”,有大量国内优秀 UP 制作的免费视频课程,非常适合入门。

- CSDN / 博客园:搜索具体问题,如 “FIFO 读写空满判断”、“Verilog 状态机写法”,可以找到大量技术博客和项目分享。

- FPGA Forum (原 Altera 论坛):Intel 官方技术论坛,遇到疑难问题时可以在这里提问。

- GitHub:搜索

FPGA-Verilog-Projects等关键词,可以找到大量开源的 FPGA 项目代码,是学习优秀代码风格的绝佳途径。

-

经典书籍

- 《Verilog 数字系统设计教程》(夏宇闻等):国内经典的 Verilog 入门书籍。

- 《FPGA 原理与工程应用》(潘松等):理论与实践结合得很好。

- 《FPGA 权威指南》(Clive Maxfield):内容非常有趣,从历史讲起,激发学习兴趣。

第五部分:学习建议与避坑指南

- 从点亮 LED 开始:永远不要跳过最简单的步骤,确保你的开发环境、硬件连接、烧录流程是通的。

- 仿真!仿真!仿真!:养成先仿真、后综合的好习惯,功能仿真是保证设计正确性的最有效手段。

- 模块化设计:将大项目分解为小模块,逐个模块设计、仿真、验证,最后再进行顶层集成,这会让你的思路更清晰,调试更容易。

- 理解时序:FPGA 设计的核心挑战之一是时序问题,学习建立时间 和保持时间 的概念,理解时序报告,学会看关键路径。

- 善示波器和逻辑分析仪:当仿真正确但硬件不工作时,示波器是调试硬件接口(如 SPI, I2C)的必备工具。

- 耐心和毅力:FPGA 学习曲线较陡,遇到问题是常态,不要气馁,学会查阅资料、分析问题、耐心调试,这个过程本身就是最好的学习。

祝您在 Altera (Intel) FPGA 的世界里探索愉快!