Cadence IC 设计全流程教程

第一部分:基础准备与环境搭建

在开始之前,你需要准备好以下环境和工具:

-

硬件:

- 一台性能较好的电脑(推荐 CPU i5/R5 以上,内存 16GB 以上,SSD 硬盘)。

- 远程服务器:强烈建议连接到实验室或公司的服务器,因为 Cadence 软件非常庞大,对本地机器性能要求高,且服务器上通常已预装好所有库和工具。

-

软件:

- Cadence Virtuoso:核心的版图和 schematic 编辑工具。

- Cadence Spectre/PSpice:主要的电路仿真器。

- 其他工具:如用于版图提取的 Diva/Assura,用于后仿的 Virtuoso AMS 等。

-

库文件:

- 这是最关键的一步!你需要从你的导师、公司或 PDK 提供商那里获得工艺设计套件。

- PDK (Process Design Kit):包含了特定工艺下所有元器件的模型、设计规则、版图符号、DRC/LVS 检查规则等,没有 PDK,你无法进行任何有效的设计。

- 标准单元库:对于数字设计或混合信号设计,还需要预定义好的标准单元库。

-

学习资料:

(图片来源网络,侵删)

(图片来源网络,侵删)- PDK 自带的文档:这是最权威的资料,一定要仔细阅读。

- Cadence 官方文档:搜索 Cadence Online Support。

- 经典教材:

- 《CMOS Analog Circuit Design》 by P. E. Allen, D. R. Holberg

- 《Design of Analog CMOS Integrated Circuits》 by Behzad Razavi

- 《Analysis and Design of Analog Integrated Circuits》 by Paul R. Gray, etc.

第二部分:核心流程详解

我们将以一个经典的 运算放大器 设计为例,走完整个流程。

电路设计与仿真

这是设计的起点,目标是验证电路的功能和性能指标。

步骤 1:创建新库

- 打开 Cadence Virtuoso (

virtuoso &)。 - 在 CIW (Command Interpreter Window) 窗口中,执行

File -> New -> Library。 - 输入库名(

my_opamp_lib),选择Attach to an existing techfile,然后从 PDK 列表中选择你工艺对应的techfile。 - 点击

OK。

步骤 2:绘制电路图

- 在库管理器中,右键点击你的库名,选择

New -> Cellview。 - 在弹出的窗口中,Cell Name 填入

opamp_schematic,Tool 选择Composer-Schematic,点击OK。 - 此时会出现 Schematic Editing 窗口。

- 添加元器件:

- 点击左侧工具栏的

Instance(快捷键i)。 - 在

Component Browser中,浏览你的 PDK 库,找到需要的晶体管(如nmos4,pmos4)、电阻、电容等。 - 放置元器件并设置其参数(如 W, L)。

- 点击左侧工具栏的

- 连接导线:

- 点击

Wire(快捷键w) 或Pin(快捷键p) 进行连接。

- 点击

- 添加端口:

- 点击

Pin,添加输入 (in+,in-)、输出 (out)、电源 (VDD)、地 (VSS) 等端口。

- 点击

- 保存:快捷键

Ctrl + S。

步骤 3:设置仿真环境

我们需要使用仿真器来测试这个电路,这里以 Spectre 为例。

- 在 Schematic Editing 窗口中,执行

Tools -> Annotate -> Netlist,生成网表。 - 创建一个新的 Cellview,类型为

Cellview,Tool 选择ADE L(Analog Design Environment L),这是 Spectre 仿真器的主界面。 - 设置变量:

- 在 ADE L 界面,点击

Variables->Copy from Cellview,将原理图中的变量(如 MOS 的 W, L)导入。 - 你也可以在这里定义新的仿真变量,如

temperature(温度)。

- 在 ADE L 界面,点击

- 选择仿真器:

- 在 ADE L 界面,确保

Simulator选项卡中选择的仿真器是spectre。

- 在 ADE L 界面,确保

- 设置分析:

- 点击

Analyses按钮。 - DC 分析:用于直流工作点扫描。

- 添加

dc分析。 - 在

Variable中选择vss(或你定义的电源变量),Start设为0,Stop设为8(假设 VDD=1.8V),Step设为01。

- 添加

- AC 分析:用于频率响应分析。

- 添加

ac分析。 Sweep Type选择decade,Start Frequency设为1,Stop Frequency设为1G,Points per decade设为10。- 在

Signal标签页,设置交流激励源,通常在输入端口加一个VAC源,幅度设为1。

- 添加

- 瞬态分析:用于时域响应分析。

- 添加

tran分析。 Stop Time设为1u,Step Size设为1p。

- 添加

- 点击

步骤 4:运行仿真并查看结果

- 在 ADE L 界面,点击绿色的

Run按钮开始仿真。 - 仿真结束后,会自动弹出

Waveform Viewer(波形查看器) 窗口。 - 添加波形:

- 在左侧的

Results Browser中,展开你需要的节点电压或电流。 - 选中并拖动到右侧的波形显示区域。

- 在左侧的

- 计算性能指标:

- 直流增益:在 AC 分析结果中,找到输出和输入的波形,使用

Calculator工具 (Tools -> Calculator) 计算db(vout("/out"))的最大值。 - 相位裕度:在 Calculator 中,使用

phase(vout("/out"))和group_delay(...)等函数计算。 - 单位增益带宽:找到增益下降到 0dB 时的频率点。

- 压摆率:在瞬态分析中,给运放一个大的阶跃输入,观察输出电压的变化速率

dvdt(vout("/out"))。

- 直流增益:在 AC 分析结果中,找到输出和输入的波形,使用

这个“设计-仿真-优化”的迭代过程是模拟 IC 设计的核心,你需要根据仿真结果,不断调整电路结构和元器件参数,直到满足所有设计指标。

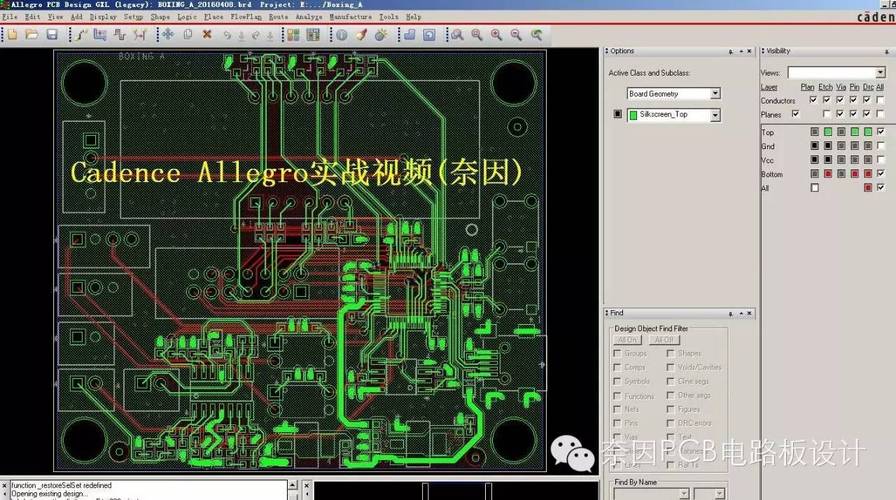

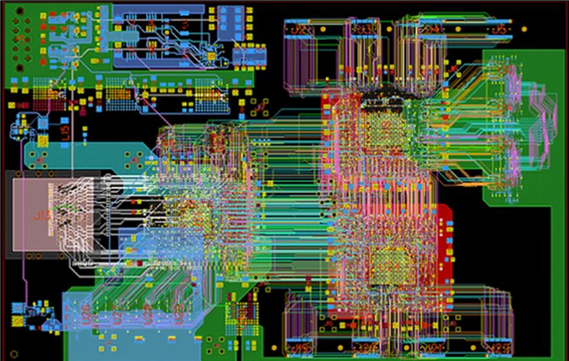

版图设计与验证

当电路仿真通过后,就需要将设计转化为可以制造的物理版图。

步骤 5:创建新 Cellview

- 在库管理器中,右键点击你的库名,选择

New -> Cellview。 - Cell Name 填入

opamp_layout,Tool 选择Virtuoso,点击OK。 - 这时会打开 Layout Editing 窗口。

步骤 6:绘制版图

- 设置显示图层:在 LSW (Layer Selection Window) 中,勾选你工艺需要的图层(如

nwell,pwell,poly,metal1,metal2等)。 - 摆放元器件:

- 从库中找到元器件的

layout view(通常是L或layout。 - 使用

Instance工具 (i) 将其放置到版图编辑区。 - 调整元器件的位置和方向,使其布局紧凑、连线最短。

- 从库中找到元器件的

- 绘制连线:

- 使用

Drawing工具 (w,r,s等) 在相应的金属层上绘制导线,连接元器件的端口。 - 注意:版图中的连线必须和原理图中的连接关系完全一致。

- 使用

- 添加衬底/阱接触:为所有 MOS 管添加合适的

Well Tap和Substrate Contact,以确保衬电位的稳定。 - 添加保护环:在敏感电路周围添加

Guard Ring以提高抗噪声能力。 - 放置焊盘:在版图边界放置

Pad,用于与外界连接。 - 保存:快捷键

Ctrl + S。

步骤 7:版图验证

这是确保版图“正确”和“可制造”的关键步骤。

-

DRC (Design Rule Check) - 设计规则检查:

- 目的:检查版图是否满足工艺厂商规定的最小尺寸、间距等规则。

- 操作:在 Layout Editing 窗口中,执行

Verification -> DRC。 - 选择正确的 DRC 规则文件(通常在 PDK 中),然后运行。

- 如果有错误,DRC Report 会列出所有违规之处,你需要返回版图进行修改,直到 DRC 通过。

-

LVS (Layout Versus Schematic) - 版图原理图对比:

- 目的:检查版图的电气连接关系是否与原理图完全一致。

- 操作:在 Layout Editing 窗口中,执行

Verification -> LVS。 - 选择正确的 LVS 规则文件,并指定你的原理图 Cellview (

opamp_schematic)。 - 运行 LVS,如果通过,会提示

LVS Matched,如果不通过,会列出差异,如短路、开路、元器件参数不匹配等,需要仔细排查和修改。

后仿真

版图验证通过后,还不能保证芯片性能,因为版图中的寄生参数(如连线电阻、电容)会严重影响电路的高频性能,必须进行后仿真。

步骤 8:提取寄生参数

- 在 Layout Editing 窗口中,执行

Tools -> Parasitic Extraction。 - 选择提取工具(如

Assura或QRC)和相应的规则文件。 - 运行提取,工具会生成一个包含所有寄生参数的网表文件(通常是

.sp或scs格式)。

步骤 9:运行后仿真

- 回到 ADE L 环境。

- 加载新的网表:在

Setup -> Simulator/Directory/Host...中,将网表路径指向你刚刚提取出的寄生参数网表。 - 重新运行仿真:使用和前仿真完全相同的设置(AC, Transient 分析)再次运行仿真。

- 对比结果:将后仿的波形与前仿波形放在同一个 Waveform Viewer 中对比。

- 如果后仿的性能(如增益、带宽、相位裕度)显著下降,说明寄生效应影响很大,需要返回版图阶段进行优化(如增大连线宽度、调整布局等)。

- 重复“版图优化-提取-后仿真”的循环,直到后仿结果满足设计指标。

第三部分:进阶与技巧

- 脚本自动化:学习使用 Skill 语言编写脚本,可以自动完成重复性任务,如批量修改参数、生成报告等,极大提高效率。

- 参数化单元:将常用的电路结构(如电流镜、差分对)创建为 Pcell,可以通过参数灵活调整其尺寸和特性。

- 版图规划:在绘制复杂版图前,先进行规划,确定核心模块、电源、地的布局,这会对最终性能和布线难度产生巨大影响。

- 电源地网络分析:使用

Voltus或RedHawk等工具进行 IR Drop 和 EMI 分析,确保电源的稳定性。

学习资源推荐

- Bilibili:搜索“Cadence 教程”、“Virtuoso 教程”、“Spectre 教程”,有大量优秀的中文视频教程。

- YouTube:搜索 "Cadence Virtuoso tutorial for beginners","Analog IC design flow",有大量高质量的英文视频。

- EDA365 论坛:国内非常活跃的 EDA 交流社区,可以找到很多学习资料和问题解答。

- 学校课程:很多大学的微电子专业都开设了 IC 设计相关的实验课程,可以跟着老师的指导进行学习。

也是最重要的一点:

实践是掌握 Cadence 的唯一途径,不要害怕犯错,大胆地去尝试、去仿真、去画版图,每一次 DRC/LVS 的报错,每一次仿真的失败,都是你学习和进步的机会。

祝你学习顺利!