Quartus Prime 完整入门教程

目录

- 准备工作

- 1 什么是 Quartus Prime?

- 2 下载与安装

- 3 准备硬件与软件环境

- 创建第一个工程

- 1 启动 Quartus Prime

- 2 使用新建项目向导

- 3 设置工程信息

- 4 选择器件

- 5 设置 EDA 工具(可选)

- 6 完成项目创建

- 设计输入:使用原理图

- 1 创建新文件

- 2 使用图形编辑器

- 3 保存文件

- 4 添加文件到工程

- 编译与综合

- 1 启动编译器

- 2 查看编译报告

- 3 分析错误与警告

- 功能仿真

- 1 创建 Vector Waveform File (.vwf)

- 2 添加输入输出节点

- 3 设置输入波形

- 4 运行仿真

- 5 分析仿真结果

- 引脚分配

- 1 打开引脚规划器

- 2 分配引脚

- 3 重新编译

- 生成编程文件与硬件测试

- 1 生成 SOF 文件

- 2 使用 Quartus Prime Programmer

- 3 下载到 FPGA

- 总结与进阶

准备工作

1 什么是 Quartus Prime?

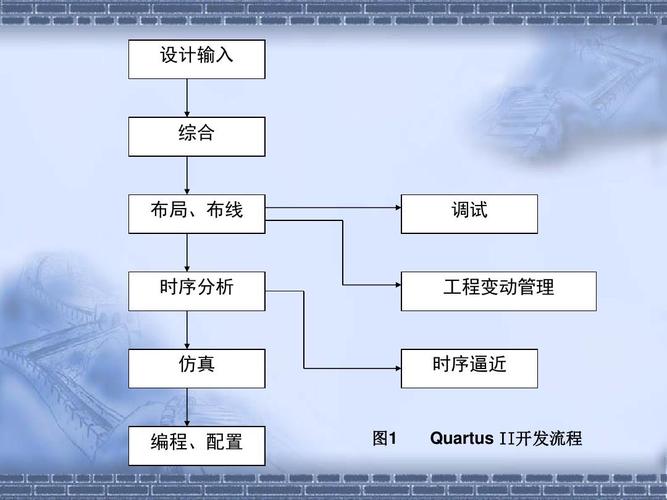

Quartus Prime 是 Intel(原 Altera)公司为其 FPGA(现场可编程门阵列)和 CPLD(复杂可编程逻辑器件)提供的一套综合性、集成的开发软件,它集成了设计输入、逻辑综合、仿真、时序分析、布局布线、编程等一系列功能,是 FPGA 开发的核心工具。

2 下载与安装

- 访问官网:打开浏览器,访问 Intel 官网 FPGA 开发软件页面:https://www.intel.com/content/www/us/en/software/programmable/quartus-prime/download.html

- 选择版本:选择 "Quartus Prime Lite Edition",这是免费版本,功能足够满足学习和大多数中小型项目开发。

- 填写信息:填写必要的个人信息并同意许可协议,即可下载安装包,文件较大,请耐心等待。

- 安装:

- 运行下载的安装包(

QuartusPrimeSetup-23.1std.1.950-windows.exe)。 - 按照安装向导的提示进行操作。强烈建议保持默认安装路径,不要使用中文路径或带有空格的路径。

- 在安装过程中,会提示你安装额外的组件,对于初学者,建议勾选 "Device Support",并选择你计划使用的 FPGA 器件系列(Cyclone IV, Cyclone V, Cyclone 10 LP 等),如果不确定,可以全部安装。

- 安装完成后,重启电脑。

- 运行下载的安装包(

3 准备硬件与软件环境

- 硬件:为了进行硬件测试,你需要一块 FPGA 开发板,对于初学者,推荐使用 Cyclone IV 或 Cyclone V 系列的开发板,如 Terasic DE0/DE1/DE2 系列,或国内的一些教育板卡。

- 软件:

- Quartus Prime:已安装。

- USB 驱动:开发板通常会附带 USB 驱动,用于将程序下载到 FPGA,请根据开发板说明书安装。

- 文本编辑器:除了原理图,我们还会用 Verilog/VHDL 进行设计,可以使用任何文本编辑器,如 Notepad++, VS Code, 或者 Quartus Prime 自带的文本编辑器。

创建第一个工程

我们将创建一个简单的工程,目标是点亮一个 LED 灯。

1 启动 Quartus Prime

安装完成后,从开始菜单启动 "Quartus Prime (Version xx.x)"。

2 使用新建项目向导

- 启动后,点击主界面上的

File->New Project Wizard...。 - 在欢迎界面,点击

Next。

3 设置工程信息

- Directory, Name, Top-Level Entity:

- Directory: 选择一个你用来存放工程的文件夹。

- Name: 为你的工程起一个名字,

led_blink。 - Top-Level Entity: 这是你设计的最高模块名称,通常和工程名保持一致,Quartus 会自动填充,点击

Next。

4 选择器件

这是最关键的一步,必须根据你的开发板来选择。

- 在 Family 下拉菜单中,选择你的开发板所用的 FPGA 系列(

Cyclone IV E)。 - 在 Available devices 列表中,根据开发板手册,选择具体的器件型号(

EP4CE6E22C8)。 - 在右侧的 Filters 中,你可以通过封装、速度等级等进一步筛选。

- 确认选中正确的器件后,点击

Next。

5 设置 EDA 工具(可选)

EDA 工具是第三方的高级仿真、综合工具,对于初学者,我们使用 Quartus 自带的工具,所以直接点击 Next,跳过此步骤。

6 完成项目创建

- 在最后一步,会显示一个项目摘要,确认无误后,点击

Finish。 - Quartus 会自动打开工程,并显示一个空白的界面,至此,一个空的 FPGA 工程已经创建好了。

设计输入:使用原理图

我们将用原理图的方式设计一个将输入时钟分频,驱动 LED 闪烁的电路。

1 创建新文件

- 点击

File->New。 - 在弹出的对话框中,选择

Block Diagram/Schematic File,然后点击OK。 - 一个空的图形编辑器窗口会打开。

2 使用图形编辑器

-

放置元件:

- 在图形编辑器窗口的任意位置,双击鼠标左键。

- 弹出

Symbol对话框。 - 在

Name栏中输入元件名称,或者从左侧的库中浏览。 - 我们需要一个输入引脚、一个输出引脚、一个计数器和一个门电路。

- 输入引脚:在

Name栏输入INPUT,点击OK,然后在图纸上点击放置。 - 输出引脚:在

Name栏输入OUTPUT,点击OK,然后在图纸上点击放置。 - 计数器:在

Name栏输入lpm_counter,这是 Altera 提供的一个参数化模块库,点击OK放置。 - 门电路:在

Name栏输入AND2(一个2输入与门),点击OK放置。

-

连接导线:

- 将鼠标移动到元件的引脚上,鼠标会变成十字形。

- 按住鼠标左键拖动到另一个引脚或导线上,松开即可连接。

- 设计思路:

- 将

INPUT引脚连接到lpm_counter的时钟输入clk。 - 将

lpm_counter的某个输出位(q[0],一个较低位的计数)连接到AND2的一个输入端。 - 将

AND2的另一个输入端连接到lpm_counter的另一个输出位(q[20],一个较高位的计数,用于降低闪烁频率)。 - 将

AND2的输出连接到OUTPUT引脚。

- 将

-

设置参数:

(图片来源网络,侵删)

(图片来源网络,侵删)- 双击图上的

lpm_counter元件,打开参数设置对话框。 - 设置

lpm_width(计数器位数),例如设置为24。 - 确保其他参数(如

lpm_direction)设置正确。 - 点击

OK保存。

- 双击图上的

3 保存文件

点击 File -> Save As,将文件命名为 led_blink.bdf,并保存到工程文件夹中。

4 添加文件到工程

- 在 Quartus 界面左侧的

Project Navigator窗口中,右键点击Files。 - 选择

Add/Remove Files in Project...。 - 在弹出的对话框中,点击

Add All,然后点击OK,这样就把刚刚创建的led_blink.bdf文件添加到工程中了。

编译与综合

编译过程将你的设计(原理图或代码)转换成 FPGA 能够理解的底层配置。

1 启动编译器

点击工具栏上的 Start Compilation 按钮(一个向下的箭头图标),或者通过 Processing -> Start Compilation 启动。

2 查看编译报告

编译成功后,会自动弹出 Compilation Report,这个报告非常重要,它包含了编译过程中的所有信息。

3 分析错误与警告

- 绿色对勾:表示编译成功。

- 黄色感叹号:表示有警告,警告通常不影响最终功能,但可能影响设计质量,需要关注。

- 红色叉号:表示有错误,错误必须修复,否则无法生成最终文件。

如果出现错误,双击报告中的错误信息,Quartus 会自动跳转到设计文件中对应的错误位置,帮助你进行修改。

功能仿真

仿真是在电脑上模拟你的设计逻辑是否正确,而不需要下载到硬件上。

1 创建 Vector Waveform File (.vwf)

- 点击

File->New。 - 选择

Vector Waveform File,点击OK。 - 一个波形编辑器窗口会打开。

2 添加输入输出节点

- 在波形编辑器左侧的

Name区域空白处,右键点击,选择Insert->Insert Node or Bus...。 - 在弹出的对话框中,点击

Node Finder...按钮。 - 在

Filter中选择Pins: all,然后点击List。 - 下方的

Nodes Found列表会显示你设计中的所有输入输出引脚,选中它们,然后点击> >将其添加到右侧的Selected Nodes & Groups列表中。 - 点击

OK,再点击OK关闭对话框,你的输入输出引脚都出现在波形编辑器中了。

3 设置输入波形

- 在

Name列中选中你的输入引脚(INPUT)。 - 在工具栏上找到设置波形为高电平(

Logic 1)或低电平(Logic 0)的按钮。 - 为了模拟时钟,我们可以使用

Edit->Value->Clock...。- 选中

INPUT引脚。 - 点击

Clock...。 - 设置

Period为周期,0 ns(对应 20MHz 频率),然后点击OK,你会看到输入波形变成了周期性的方波。

- 选中

4 运行仿真

-

指定仿真器设置:点击

Assignments->Settings。 -

在左侧选择

EDA Tool Settings->Simulation。 -

在

NativeLink settings中,确保Compile test bench是勾选的。 -

点击

Test Benches...。 -

在弹出的窗口中,点击

New...。 -

输入一个测试平台名称,然后在

Top-level module in test bench中输入你的顶层模块名led_blink。 -

点击

Add->File,然后浏览并选择一个.v或.vhd的测试平台文件。注意:Quartus Lite 自带的仿真器 ModelSim-Altera 需要一个 Verilog 或 VHDL 格式的测试平台,Quartus 默认不生成,你需要手动编写一个简单的测试平台文件,或者使用第三方仿真器,对于初学者,这一步可能比较复杂,一个更简单的方法是使用Generate Functional Simulation Netlist功能:- 在

Processing菜单下,确保勾选了Generate Functional Simulation Netlist。 - 然后直接运行仿真。

- 在

-

启动仿真器:点击工具栏上的

Start Simulation按钮(一个带波形的箭头图标)。

5 分析仿真结果

仿真完成后,波形窗口会显示输出信号(OUTPUT)随时间变化的情况。

- 观察

OUTPUT的波形是否按照你的预期变化(在INPUT时钟的驱动下,OUTPUT信号以一个非常低的频率闪烁)。 - 如果波形不正确,你需要回到设计阶段(原理图或代码)检查逻辑,然后重新编译和仿真。

引脚分配

引脚分配就是告诉 Quartus,你设计中的 INPUT 和 OUTPUT 信号应该连接到开发板上的哪个物理引脚。

1 打开引脚规划器

点击 Assignments -> Pin Planner。

2 分配引脚

- 在

Pin Planner窗口中,你会看到两列:Node Name(你的设计信号名)和Location(物理引脚号)。 - 在

Location列中,双击空白处,从下拉列表中选择开发板手册中指定的引脚号。- 如果开发板手册说 LED 连接到

PIN_P11,那么就在OUTPUT信号对应的Location单元格中输入P11。 - 如果有一个按键连接到

PIN_N2,那么就在INPUT信号对应的Location单元格中输入N2。

- 如果开发板手册说 LED 连接到

- 注意:你必须查阅你的开发板用户手册来获取正确的引脚分配信息。

3 重新编译

引脚分配后,必须重新编译工程,这些信息才会被加入到最终的配置文件中,点击 Start Compilation。

生成编程文件与硬件测试

1 生成 SOF 文件

编译成功后,Quartus 会生成多种格式的编程文件,对于大多数 Intel 开发板,我们使用 .sof (SRAM Object File) 文件。

- 这个文件在编译完成后,通常会自动生成在工程目录下的

output_files文件夹中,文件名如led_blink.sof。

2 使用 Quartus Prime Programmer

- 点击

Tools->Programmer。 - Programmer 窗口是空的,点击

Add File...,然后选择刚刚生成的led_blink.sof文件。 - 确保

Hardware Setup...中选择的硬件是正确的(通常是连接到电脑的 USB-Blaster 适配器),如果看不到,可以点击Auto Detect。 - 在左侧文件列表中,确保勾选了

led_blink.sof。 - 点击

Start按钮。

3 下载到 FPGA

如果一切顺利,进度条会走完,并显示 "Success!"。

恭喜! 你的 FPGA 开发板上的 LED 灯应该按照你的设计开始闪烁了!

总结与进阶

恭喜你,你已经完成了 Quartus Prime 的第一个完整设计流程!

-

我们学习了如何创建工程、使用原理图进行设计、编译、仿真、分配引脚,并最终将程序下载到 FPGA 进行验证,这是 FPGA 开发的标准流程。

-

进阶方向:

- 使用 Verilog/VHDL:原理图适合简单设计,但对于复杂系统,硬件描述语言 是主流,尝试学习 Verilog 或 VHDL,并使用 Quartus 的文本编辑器进行设计。

- IP 核使用:Quartus 提供了丰富的 IP 核(如 Nios II 处理器、DDR3 控制器等),学习如何调用和配置这些 IP 核可以大大加快开发速度。

- 时序分析:深入学习时序分析,理解建立时间和保持时间,学习如何修复时序违规。

- 更复杂的仿真:学习编写 SystemVerilog Testbench,使用更专业的仿真器如 ModelSim 进行更全面的验证。

这份教程为你打下了坚实的基础,祝你 FPGA 学习之旅顺利!