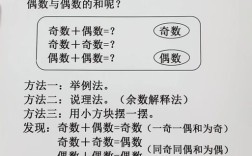

Quartus II 教程:从零开始 FPGA 开发

本教程将以 Intel(原 Altera)的 Quartus Prime 软件为例(Quartus II 是旧版名称,但操作逻辑类似),带你实现一个经典的 LED 流水灯 项目,通过这个项目,你将掌握 FPGA 开发的基本流程。

第一部分:准备工作

在开始之前,请确保你已经准备好以下几样东西:

-

硬件:

- 一块 FPGA 开发板,本教程将以常见的 DE10-Lite (Intel Cyclone 10 LP) 为例,但流程适用于大多数 Intel/Altera FPGA 开发板。

- 一根 Micro-USB 线,用于连接电脑和开发板,以及供电。

-

软件:

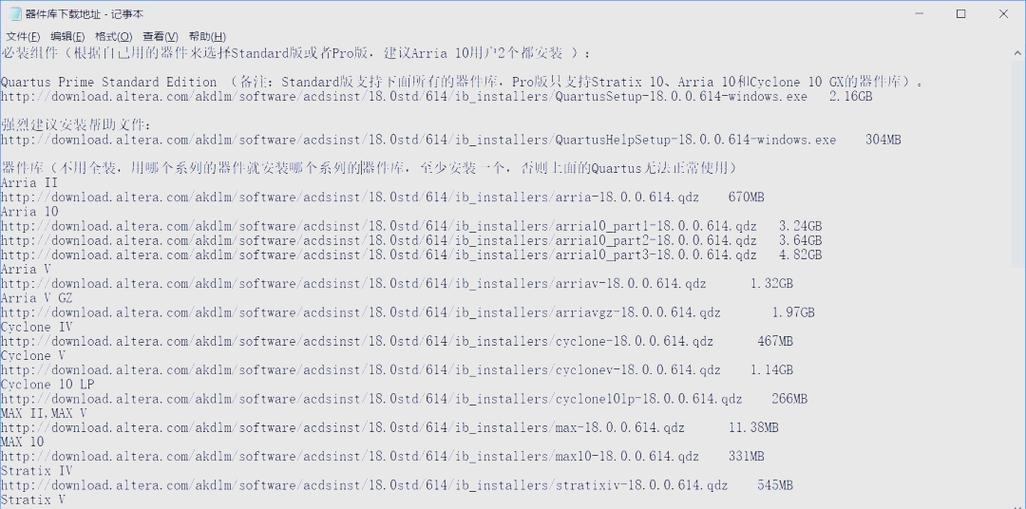

- Quartus Prime 软件:从 Intel 官网下载,你需要根据你的开发板型号选择对应的版本(如 Standard Edition 或 Lite Edition),对于初学者和教学,免费的 Lite Edition 完全足够。

- USB-Blaster 驱动:通常在 Quartus 安装包中会包含,用于将程序下载到 FPGA 芯片中。

- 文本编辑器或 IDE:你可以使用 Quartus 自带的文本编辑器,也可以使用更专业的 Verilog/VHDL 编辑器,如 VS Code + 插件。

第二部分:安装与设置

-

安装 Quartus Prime:

(图片来源网络,侵删)

(图片来源网络,侵删)- 运行下载的安装包,按照向导进行安装,在安装过程中,你可以选择安装 "Device Support",确保包含你的开发板所用的 FPGA 型号(如 Cyclone 10 LP)。

- 安装完成后,启动 Quartus Prime 软件。

-

设置 USB-Blaster:

- 将开发板通过 Micro-USB 线连接到电脑。

- 在 Windows 的设备管理器中,查看是否能找到 "USB-Blaster" 或 "JTAG" 设备,如果显示黄色感叹号,说明驱动未正确安装,你需要手动安装驱动(驱动文件通常在

Quartus\drivers\usb-blaster目录下)。

第三部分:创建新工程

这是所有工作的第一步,目的是告诉 Quartus 我们要做一个什么样的项目。

-

启动新工程向导:

- 打开 Quartus Prime,点击菜单

File->New Project Wizard...。

- 打开 Quartus Prime,点击菜单

-

填写基本信息:

- Directory, Name, Top-Level Entity:

- What is the working directory for this project?: 选择一个你用来存放项目的文件夹。

- What is the name of this project?: 给你的项目起一个名字,

led_water_flow。 - What is the name of the top-level entity in this project?: 顶层实体名,通常和项目名保持一致,

led_water_flow。 - 点击

Next。

- Directory, Name, Top-Level Entity:

-

添加文件:

- Add files:因为我们还没有创建设计文件,所以这里直接点击

Next,后续可以手动添加。

- Add files:因为我们还没有创建设计文件,所以这里直接点击

-

选择开发板/FPGA 器件:

- Family: 选择你的开发板所用的 FPGA 系列,

Cyclone 10 LP。 - Target device: 勾选

Specific device selected in 'Available devices' list。 - Available devices: 在列表中找到你的开发板上的具体芯片型号,对于 DE10-Lite,是

5CSEBA6U23I7,选中它,然后点击Next。 - 提示:如果你没有开发板,可以选择一个通用的、同系列的型号进行学习。

- Family: 选择你的开发板所用的 FPGA 系列,

-

选择 EDA 工具:

- 本教程不使用第三方 EDA 工具,所以所有选项都保持默认,直接点击

Next。

- 本教程不使用第三方 EDA 工具,所以所有选项都保持默认,直接点击

-

- 检查所有信息是否正确,然后点击

Finish完成项目创建。

- 检查所有信息是否正确,然后点击

第四部分:编写 Verilog 代码

我们来设计 LED 流水灯的逻辑。

-

创建新设计文件:

- 在左侧的

Project Navigator窗口中,右键点击led_water_flow(你的项目名) ->New->Verilog HDL File。 - 一个新的空白文件会打开。

- 在左侧的

-

编写 Verilog 代码:

- 将以下代码复制并粘贴到新文件中,这段代码的功能是:在时钟信号的控制下,让 8 个 LED 灯像流水一样循环点亮。

// =================================================================== // --- Project Name: led_water_flow // --- Author: [Your Name] // --- Description: LED Water Flow on DE10-Lite // =================================================================== `timescale 1ns / 1ps // 定义时间尺度 module led_water_flow ( input CLOCK_50, // 50MHz 时钟输入 input KEY, // 按键,作为复位信号 output [7:0] LED // 8 个 LED 输出 ); // ------------------------------------------------------------------- // 内部信号定义 // ------------------------------------------------------------------- reg [25:0] counter; // 分频计数器 reg [2:0] led_pattern; // LED 流水灯模式 wire clk_1Hz; // 1Hz 的时钟信号,用于控制流水灯速度 // ------------------------------------------------------------------- // 分频模块:将 50MHz 分频为 1Hz // 50,000,000 / 2 - 1 = 24,999,999 // ------------------------------------------------------------------- always @(posedge CLOCK_50 or negedge KEY) begin if (!KEY) begin // 当按键按下时,复位计数器 counter <= 26'd0; end else begin if (counter == 26'd24_999_999) begin counter <= 26'd0; end else begin counter <= counter + 1; end end end // 产生 1Hz 的时钟信号 assign clk_1Hz = (counter == 26'd24_999_999); // ------------------------------------------------------------------- // 流水灯控制逻辑 // ------------------------------------------------------------------- always @(posedge clk_1Hz or negedge KEY) begin if (!KEY) begin // 当按键按下时,复位 LED 状态 led_pattern <= 3'b001; // 初始状态,只点亮第一个 LED end else begin // 循环移位:001 -> 010 -> 100 -> 001 ... led_pattern <= {led_pattern[1], led_pattern[0], led_pattern[2]}; end end // ------------------------------------------------------------------- // LED 输出逻辑 // 将 3 位的 led_pattern 扩展到 8 位的 LED 输出 // 假设 LED 是低电平点亮 // ------------------------------------------------------------------- assign LED = ~{5'b00000, led_pattern}; // 高 5 位灭,低 3 位受 led_pattern 控制 endmodule- 代码解释:

module ... endmodule: Verilog 的基本结构,定义了一个名为led_water_flow的模块。input,output: 定义模块的输入输出端口。CLOCK_50是开发板上的 50MHz 晶振,KEY是一个复位按键,LED是连接到 8 个灯的输出。reg,wire: 定义内部信号。reg类型的信号必须在always块中赋值,wire类型的信号通过assign语句或模块实例的输出连接。always @(posedge ... or negedge ...): 这是一个过程块,在指定的边沿(时钟上升沿或按键下降沿)执行。if (!KEY): 检测按键是否按下(假设按键是低电平有效),如果按下,就执行复位操作。assign LED = ...: 将内部信号led_pattern连接到外部LED引脚。 是按位取反,因为很多开发板的 LED 是低电平点亮。

-

保存文件:

- 按

Ctrl + S,将文件保存为led_water_flow.v。

- 按

-

添加文件到工程:

- 在

Project Navigator窗口中,右键点击Files->Add/Remove Files in Project...。 - 在弹出的对话框中,选中

led_water_flow.v,点击Add->OK,确保文件出现在Files列表中。

- 在

第五部分:编译工程

编译过程包括分析、综合、适配等步骤,最终生成可以下载到 FPGA 的文件(如 .sof 文件)。

-

设置引脚分配:

- Quartus 需要知道你代码中的

CLOCK_50,KEY,LED信号连接到开发板上的具体物理引脚,这个过程叫做 引脚分配。 - 在

Assignments菜单中,选择Pin Planner。 - 在

Pin Planner窗口中,左侧是Node Name(即你代码中的信号名),右侧是Location(物理引脚号)。 - 你需要根据你的开发板 原理图 来查找每个信号对应的引脚号,然后在

Location列中手动填写。 - DE10-Lite 示例引脚:

CLOCK_50->PIN_H2KEY->PIN_J15(这是一个按键,通常低电平有效)LED[0]->PIN_AE23LED[1]->PIN_AF23LED[2]->PIN_AB21LED[3]->PIN_AC22LED[4]->PIN_AD22LED[5]->PIN_AD23LED[6]->PIN_AD24LED[7]->PIN_AE24

- 注意:引脚号务必准确,否则硬件无法正常工作。

- Quartus 需要知道你代码中的

-

运行全编译:

- 点击工具栏上的 Start Compilation 按钮(一个向下的箭头),或者按

Ctrl + L。 - 编译过程会显示进度,这可能需要几分钟时间。

- 如果编译成功,在弹出的对话框中点击

OK,你可以在左侧的Compilation Report中查看详细信息,包括资源占用情况、时序分析结果等。

- 点击工具栏上的 Start Compilation 按钮(一个向下的箭头),或者按

第六部分:仿真(可选,但推荐)

在下载到硬件之前,通过仿真验证设计的逻辑是否正确。

-

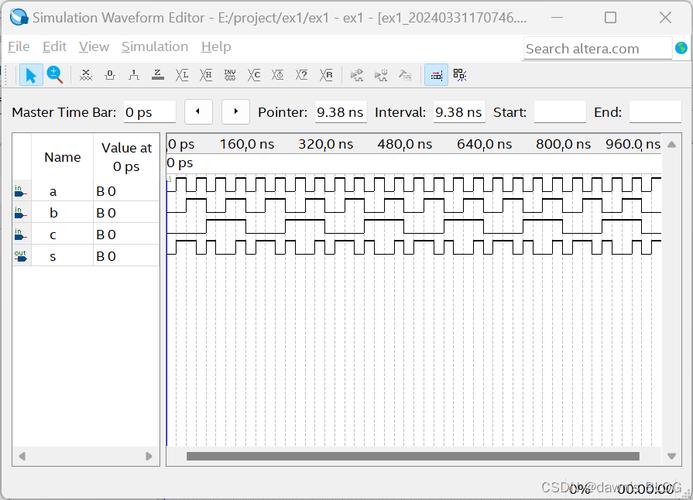

创建 Vector Waveform File (VWF):

- 在

File菜单中,选择New->Vector Waveform File。 - 一个新的波形编辑窗口会打开,保存为

led_water_flow.vwf。

- 在

-

添加节点:

- 在左侧的

Name区域双击,或者右键选择Insert->Insert Node or Bus...。 - 在弹出的对话框中,点击

Node Finder...。 - 在

Filter中选择Pins: all,然后点击List。 - 你会看到所有输入输出引脚,选中

CLOCK_50,KEY,LED,点击>>将它们添加到右侧的Selected Nodes列表中,然后点击OK->OK。

- 在左侧的

-

设置输入波形:

- 设置时钟:选中

CLOCK_50,在左侧工具栏中找到时钟设置工具(像一个方波符号),设置周期为20ns(对应 50MHz)。 - 设置复位信号:选中

KEY,在波形区域的前 100ns 内,将其设置为1(高电平,表示按键未按下),然后从 100ns 开始,将其设置为0(低电平,模拟按键按下),持续一段时间后再拉回1。 - 设置输出:

LED是输出,你不需要设置它的值,Quartus 仿真器会根据你的逻辑计算出来。

- 设置时钟:选中

-

运行仿真:

- 在

Processing菜单中,选择Start Simulation。 - 仿真完成后,波形窗口会显示所有信号的波形。

- 观察结果:放大时间轴,你应该能看到在

KEY释放后,LED的值按照11111110->11111101->11111011... 的规律变化,实现了流水灯效果。

- 在

第七部分:下载到 FPGA

如果编译和仿真都通过,就可以将你的设计“烧录”到 FPGA 芯片里了。

-

打开编程器:

- 在

Tools菜单中,选择Programmer。

- 在

-

添加文件:

- 在

Mode下拉菜单中,选择JTAG。 - 点击

Add File...,在工程目录下的output_files文件夹中找到led_water_flow.sof文件并打开。 - 确保

led_water_flow.sof文件出现在列表中,并且勾选了Program/Configure复选框。

- 在

-

连接硬件并编程:

- 确保 USB-Blaster 已经连接并识别。

- 点击工具栏上的 Start 按钮。

- 如果一切正常,进度条会走完,并显示

Success!。

-

观察结果:

你的开发板上的 8 个 LED 应该开始像流水灯一样闪烁了!按下 KEY 按键,LED 灯应该会复位到初始状态。

总结与进阶

恭喜你!你已经成功完成了第一个 FPGA 项目,并掌握了 Quartus II (Quartus Prime) 的核心工作流程:

- 创建工程

- 编写 HDL 代码

- 分配引脚

- 编译

- 仿真(可选)

- 下载

进阶学习方向:

- 更复杂的逻辑:尝试实现 4 位加法器、数码管显示、按键消抖等。

- 学习 IP 核:Quartus 提供了大量现成的 IP 核(如 PLL 锁相环、FIFO、RAM 等),可以大大加快开发速度。

- 学习时序分析:理解建立时间和保持时间,这是保证 FPGA 设计稳定运行的关键。

- 其他硬件描述语言:学习 VHDL,它是另一种广泛使用的 HDL。

这份教程为你打下了坚实的基础,接下来就需要通过更多的实践来深入探索 FPGA 的奇妙世界了,祝你学习愉快!